Produkte, deren Verkauf abgeschlossen ist.

MENU

- Startseite

- Alles sehen

- 3D Drucker

- Mini-Computer

- Elektronische Bauteile

- Sensoren

- Roboter und Mechanik

- Werkzeuge

- Smart Home

- Der Rest

- 3D DRUCKEN

- Alles sehen

- 3D-Drucker

- Filamente

- Zubehör für 3D-Drucker

- Ersatzteile für 3D-Drucker

- Kreativ-Kits für 3D-Projekte

- Glühfadentrockner

- Nachbearbeitung und Filamentverbindung

- Harze für 3D-Drucker

- Bauteile für den Bau von 3D-Druckern

- 3D-Scanner

- 3D-Stifte

- CNC

- MINICOMPUTER

- Alles sehen

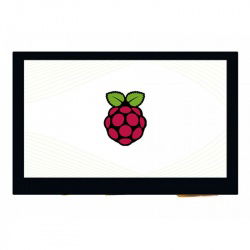

- Raspberry Pi

- Arduino

- Nvidia

- Edge AI

- Flipper Zero

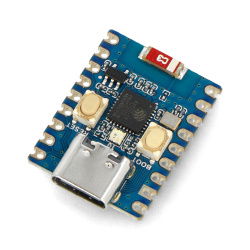

- XIAO

- Odroid

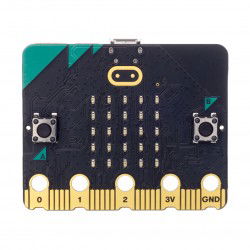

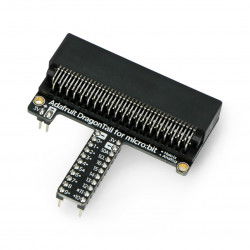

- BBC micro:bit

- Sonstige Minicomputer

- M5Stack

- ESP32

- PLCs

- ELEKTRONISCHE BAUTEILE

- Alles sehen

- Computerzubehör

- Autozubehör

- Kühlung

- Leuchtdioden

- Klang und Akustik

- Baugruppenelektronik

- Passive Elemente

- Intelligente Kleidung

- Kameras

- Konsolen

- Speicherkarten und Datenträger

- Kommunikation

- Konverter

- Kurse im Bereich Elektronik

- Mikrocontroller

- Tierabwehrgeräte

- LED-Beleuchtung

- Programmwahlschalter

- Relais, Arduino-Relais

- Spannungsregler

- Künstliche Intelligenz

- Motor- und Servo-Steuerungen

- Integrierte Schaltkreise

- Displays und Bildschirme

- Mehr...

- SENSOREN

- Alles sehen

- Alarmsensoren

- Induktive Sensoren

- Piezoelektrische Sensoren

- 9DoF IMU-Sensoren

- Drucksensoren

- Sauerstoffsensoren

- Dämmerungssensoren

- Türsensoren

- optische Sensoren

- Gassensoren

- Neigungssensoren

- Beschleunigungssensoren

- Luftreinheitssensoren

- Geräuschsensoren

- Gestensensoren

- Induktive Näherungssensoren

- Grove-System

- Gravity-System

- Grenzwert-Sensoren

- Licht- und Farbsensoren

- Magnetische Sensoren

- Medizinische Sensoren

- Kraftsensoren

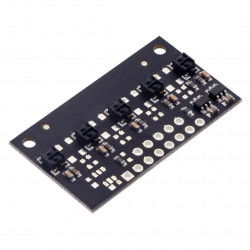

- Reflektierende Sensoren

- Abstandssensoren

- Wettersensoren

- Flüssigkeitsstand-Sensoren

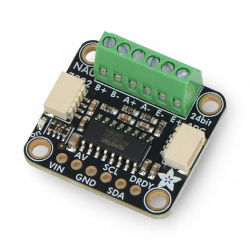

- Stromsensoren

- Durchflusssensoren

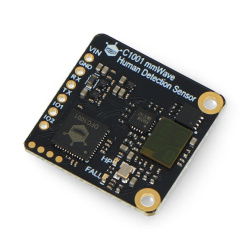

- Bewegungssensoren

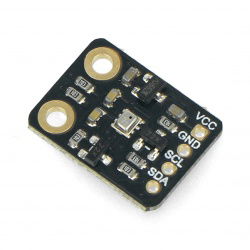

- Temperatursensoren

- PT100-Temperaturfühler

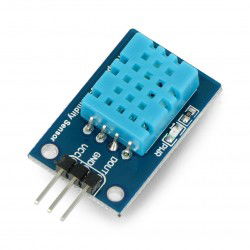

- Feuchtigkeitssensoren

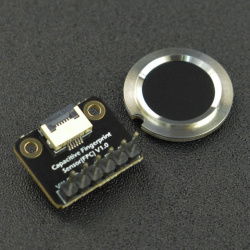

- Fingerabdruckleser

- Enkodery

- Fotowiderstände

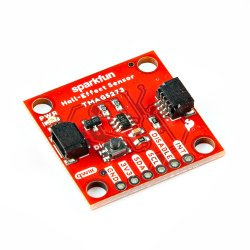

- Hall-Sensoren

- Rotationssensoren

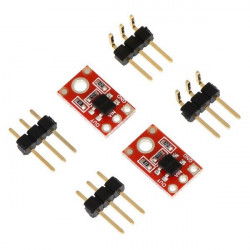

- Fototransistoren

- Infrarot-Empfänger

- Magnetometer

- Widerstandssensoren

- Gyroskope

- Sensor-Kits

- Mehr...

- ROBOTER UND MECHANISCHE BAUTEILE

- Alles sehen

- Roboter

- Servomechanismen

- Motoren

- Befestigungselemente

- Räder

- Drohnen und RC-Fahrzeuge

- SMART HOME

- Alles sehen

- Intelligente Schalter

- Intelligente Steuerungen

- Intelligente Sensoren

- Intelligente Heizung

- Intelligente Beleuchtung

- Intelligente 230-V-Steckdosen

- Zentralen und Netzwerkgateways

- Wetterstationen

- Der intelligente Garten

- Rollladen-Steuerungen

- Tor-Steuerungen

- Sprachassistenten

- IP-Videoüberwachung

- Smart Home Hersteller

- Mehr...

Neue Artikel

Rosa3D Nachfüllpackung PLA-Starterfilament 1,75 mm 1 kg – Armeegrün

Index: ROS-28112

- Neu

- Kostenloser Versand

- Neu

- Kostenloser Versand

Rosa3D Filament Nachfüllpackung PLA Starter 1,75 mm 1 kg - Weiß

Index: ROS-28125

- Neu

- Kostenloser Versand

- Neu

- Kostenloser Versand

Rosa3D Filament Nachfüllpackung PLA Starter 1,75 mm 1 kg - Schwarz

Index: ROS-28126

- Neu

- Kostenloser Versand

Sonderangebote

LattePanda V1 – 4 GB + 64 GB EEMC Intel Quad-Core-WLAN – Windows 10

Index: DFR-09376

- Ausverkauf

- Kostenloser Versand

- Sonderangebot

Filament Devil Design PLA 1,75 mm 2 kg - Weiß

Index: DEV-15238

- Reduziert

- Kostenloser Versand

- Sonderangebot

- Reduziert

- Kostenloser Versand

- Sonderangebot

- Reduziert

- Kostenloser Versand

- Sonderangebot

Elektroantrieb CAR + 1000N 10mm/s 12V - 30cm Hub

Index: ELB-19960

- Reduziert

- Kostenloser Versand

- Sonderangebot

USB-Typ-A-zu-USB-Typ-C-Konverter mit DIP-Schalter - Adafruit 5972

Index: ADA-25265

- Reduziert

- Kostenloser Versand

- Sonderangebot

Wird geladen...

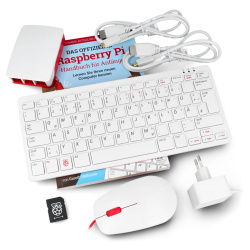

Set justPi Raspberry Pi 3B + WiFi + 32GB microSD + Zubehör

Das justPi Set beinhaltet einen Minicomputer Raspberry Pi 3 Model B + 1 GB RAM mit Schutzgehäuse und ein 5 V Netzteil mit einer Strombelastbarkeit von 2,5 A. Das Set...5.0 (23)

Index: RPI-13140

Index: RPI-13140

Auslaufprodukt

i

Nicht zugänglich

- Auslaufprodukt

- Kostenloser Versand

Auch prüfen

Was bedeutet die Angabe zur Produktverfügbarkeit?

- 1. Die auf der Produktseite angezeigte Information bezieht sich auf Bestellungen, die aktuell aufgegeben werden. Sie gilt nicht für bereits aufgegebene Bestellungen, sofern dort zu diesem Zeitpunkt eine andere Meldung angezeigt wurde.

- 2. Wenn ein konkretes Datum angegeben ist, bedeutet dies, dass wir an diesem Tag mit dem Versand aus unserem Lager beginnen; dies kann 1–2 Werktage dauern. Der Versand kann auch früher erfolgen.

- 3. Wenn ein ungefähres Datum angegeben ist (z. B. nur ein Monat), bedeutet dies, dass die Ware beim Hersteller bestellt wurde, wir aber das genaue Lieferdatum noch nicht kennen.

- 4. Die angegebenen Daten basieren auf den Angaben des Herstellers, sind vorläufig und können sich ändern.

- 5. Bitte beachte, dass wir, falls deine Bestellung mehrere nicht verfügbare Produkte enthält, diese erst versenden, wenn alle Produkte vorrätig sind.

- 6. Wenn du den Liefertermin für eine bereits aufgegebene Bestellung erfahren möchtest, wende dich bitte an unseren Kundenservice.